// ДЕМОНСТРАЦИЯ ПРОДУКТОВАКонтрактное Производство Электроники

Гибкая сборка печатной платы ДВОЙНОГО ДОСТУПА

Сборка гибких печатных плат (FPCB)

Гибкая сборка печатной платы

Гибкая сборка печатной платы

Коммуникационная сборка гибкой печатной платы

Camera Module Flex PCB Assembly

Гибкая печатная плата дисплея в сборе

Носимый гибкий узел измерения температуры

Гибкая печатная плата для медицинской электроники

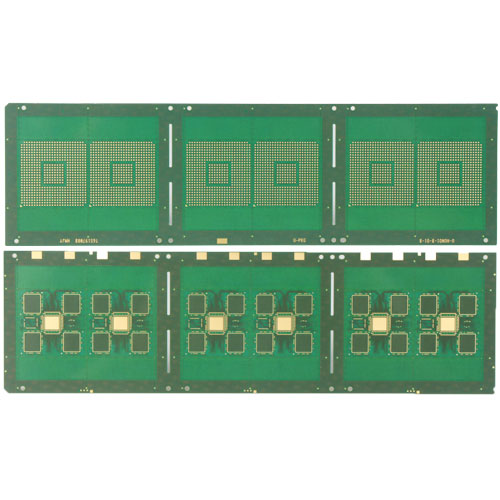

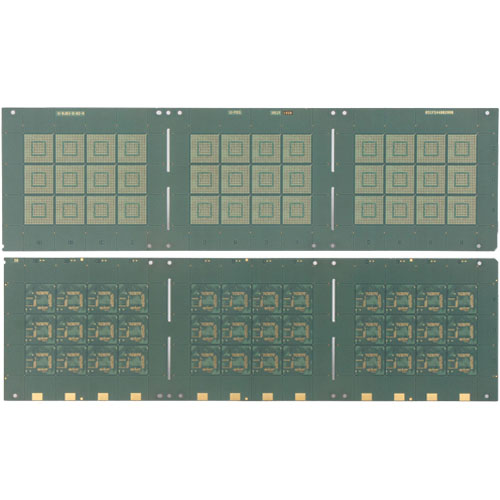

Подложка ИС

Подложки ИС представляют собой наивысший уровень миниатюризации в производстве печатных плат и имеют много общего с производством полупроводников. Технология Flip Chip является основой для упаковки высокопроизводительных интегральных схем, используемых в приложениях от смартфонов, планшетов и ПК потребительского уровня до высокопроизводительных графических рабочих станций, серверов и оборудования ИТ-инфраструктуры. Подложки ИС служат соединением между микросхемой(ами) ИС и печатной платой через проводящую сеть дорожек и отверстий.

Передовая технология, которая формирует будущее. WWPCB производит множество типов подложек ИС, на которых микросхемы ИС крепятся к подложке ИС с использованием методов проволочного соединения и/или перевернутого кристалла. Наши подложки ИС, которые производители WWPCB включают:

- CSP (корпуса масштабирования чипа)

- FC-CSP (перевернутый кристалл) CSP

- BOC (плата на чипе)

- PoP (корпус на корпусе)

- PiP (корпус в корпусе)

- SiP (система в корпусе)

- RF-модуль

- Корпус светодиода

Возможности подложек ИС:

- Количество слоев: 1L / 2L / 3L / 4L, до 22 слоев.

- Минимальная ширина линии и интервал: 9/9 мкм

- Минимальное лазерное отверстие/площадка: 45/95 мкм

- Управление импедансом для критических сигнальных трасс

- Материалы, соответствующие RoHS

- Площадка для выступов: минимальный шаг выступов 130 мкм

- Структура: любой слой, без сердечника, полость, встроенный пассивный, встроенная трасса (шаг до 20 мкм)

- Доступны широкие варианты материалов и отделки поверхности

- Толщина: 100 мкм (1,5L) ~ 225 мкм (5L)

- Наименьший размер упаковки: от 3 x 3 мм до 15 x 15 мм

Возможности подложек ИС:

- Портативные, мобильные, сетевые

- Смартфоны, бытовая электроника и DTV

- ЦП, ГП и набор микросхем для ПК-приложений

- ЦП, ГП для игровых консолей (например, X-Box, PS3, Wii…)

- Контроллер микросхем DTV, контроллер микросхем Blu-Ray

- Инфраструктурные приложения (например, сеть, базовая станция…)

- ASIC

- Цифровая полоса частот

- Управление питанием

- Графический процессор

- Контроллер мультимедиа

- Процессор приложений

- Карта памяти для продуктов 3C (например,

- Мобильные/DSC/PDA/GPS/Карманные ПК/Ноутбуки)

- Высокопроизводительные ЦП

- ГП, устройства ASIC

- Настольные компьютеры/серверы

- Сетевые

- Игровые консоли

Решения для подложек корпусов Flip Chip

Продукт представляет собой подложку корпуса, которая используется для основных полупроводников мобильных устройств и ПК. Она передает электрические сигналы между полупроводниками и основной платой и защищает дорогие полупроводники от внешнего напряжения. По сравнению с обычными подложками, поскольку эта подложка представляет собой подложку с высокой плотностью схем, содержащую больше микросхем, дефекты сборки и понесенные расходы при прямом соединении дорогих полупроводников с подложкой могут быть уменьшены.

Типы подложек для корпусов Flip Chip

Плата для упаковки интегральных схем (ИС) (ИС-субстрат) является основным компонентом упаковки интегральных схем. Она является прямым носителем для полупроводниковых зерен (DIE) и различных пассивных устройств (Passives). Она также является ключевым материалом для усовершенствованной упаковки. Плата для упаковки обеспечивает функции телекоммуникационного соединения, улучшения производительности, фиксированной поддержки, рассеивания тепла и изоляционной защиты для полупроводниковых зерен с различными пассивными устройствами. Функция является основой для реализации тонкой, миниатюрной, высокоплотной и высокопроизводительной упаковки интегральных схем.

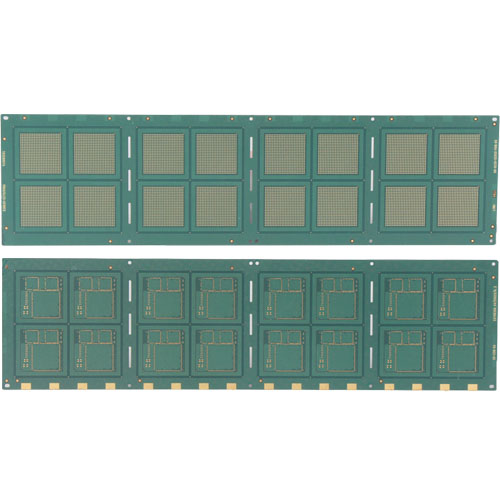

Подложка корпуса SiP

SiP (System in Package) — полупроводниковый модуль, объединяющий несколько полупроводниковых чипов и пассивных элементов в одном корпусе для достижения электрических характеристик на уровне системы.

Особенности подложки корпуса SiP

- 1,5~12 слоев, нечетные или четные слои подложек, ультратонкая подложка

- Сквозной вывод или медный столб — это последовательный процесс наращивания подложки, который можно начать и соединить на любом слое

- Большие структуры медных блоков могут быть нанесены на подложку для уменьшения падения IR и улучшения целостности питания

- Совместимость с традиционной технологией Tenting/MSAP

- Использование сквозного вывода или медного столба вместо лазерного перехода для реализации высокоплотного соединения любого слоя и любой формы

- Последовательность соединения медных столбов может улучшить производительность пакета RF и обеспечить целостность сигнала

- Сложенные в стопку медные столбы или покрытые теплоотводы создают трехмерный канал соединения для эффективного рассеивания тепла для чипа

Встроенный пакетный субстрат/модуль

Новый тип метода упаковки, при котором чип или пассивные компоненты встроены между металлическими слоями внутри подложки, а входы/выходы чипа или устройства разветвляются на внешний вывод через микроотверстия и металлические слои. Эта встроенная в чип подложка позволяет разместить на поверхности дополнительные чипы и пассивные устройства на верхней поверхности, чтобы получить более высокий интегрированный уровень функциональности в 3D-стекировании. Используя этот инновационный и настраиваемый процесс, все компоненты могут быть интегрированы в один корпус для формирования нового корпуса или модуля системного уровня.

Особенности подложки встроенного корпуса

- Встроенная в чип подложка может поддерживать 1~5 слоев разветвления и реализовывать 3D интегрированную структуру

- Бесшовное соединение между чипом и несущей платой с использованием процесса, подобного пластине, с тонкопленочным распылением Ti/Cu (Sputter Ti/Cu)

- Гибкие передовые правила проектирования позволяют достичь более тонких и меньших по размеру устройств, чем традиционный корпус полупроводника

- Изготовлено с использованием независимой интеллектуальной собственности (ИС) Hemeixin и совместимо с традиционным процессом MSAP, что обеспечивает обширную интеграцию чипа и пассивных компонентов

- Соединение между чипом и подложкой формируется путем распыления затравочного слоя тонкой металлической пленки (Ti/Cu) в процессе, подобном пластине, что значительно улучшает электрические характеристики и эффект рассеивания тепла, а также долгосрочную надежность

- Процесс представляет собой разветвление на уровне панели, которое позволяет достичь более дешевых структур, чем текущие корпуса,

- обработанные с использованием технологий Wire bond или Flip Chip

Подложка CSP (корпус чипа с проволочным соединением)

CSP (Chip Size Package) — это продукт, размер подложки корпуса которого не превышает 120% размера полупроводникового кристалла. Для уменьшения размера площади формируется CSP с очень плотной разводкой по сравнению с обычным BGA. Самая важная цель CSP — уменьшить размер монтажной области.

Упаковка масштаба чипа (CSP) использует технологию мелкого шаблона, очень маленькие переходные отверстия, сверхтонкую медную фольгу и структуру сборки для высокоплотных конструкций и гибкости. Подложка CSP обеспечивает высокую надежность как при подключении, так и при изоляции.

Применение подложки пакета CSP

- Память, аналоговая, ASIC, логика, радиочастотные устройства,

- Ноутбук, субноутбук, персональные компьютеры,

- GPS, КПК, беспроводная телекоммуникационная система

Характеристики подложки пакета CSP

- Технология точного моделирования для высокоплотного дизайна

- Структура для высокой гибкости дизайна

- Высокая надежность соединения и изоляции

- Использование материала с низким КТР, подходящего для PoP

Подложка корпуса WBCSP (Wire Bonding Chip Scale Package)

Это полупроводниковый чип, размер которого составляет более 80% от размера готовой детали. Он называется WBCSP (Wire Bonding CSP), потому что для соединения полупроводникового чипа и печатной платы применяется метод соединения золотой проволокой. Для соединения чипа и печатной платы используется золотая проволока, и возможна многокомпонентная упаковка, что делает продукт в основном применимым для микросхем памяти. В частности, продукты UTCSP (Ultra Thin CSP) изготавливаются толщиной 0,13 мм или тоньше. Благодаря высокой степени свободы в соединении чипа с печатной платой становится возможным многокомпонентная упаковка, и достигается лучшая производительность по сравнению с другими продуктами той же толщины.

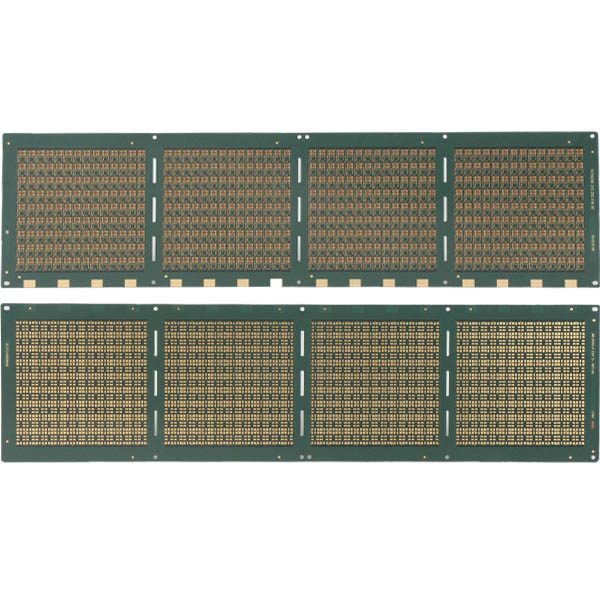

Подложка для радиочастотных модулей (Радиочастота)

Более высокий спрос на полосу пропускания частот, вызванный массовыми приложениями и мультимедиа через беспроводную связь, требует большего количества полос в телефоне. Переход на усовершенствованный протокол связи и агрегация несущих частот обуславливают спрос на количество полос, а также усилители мощности и интерфейсные модули. Радиочастотный модуль — это аналоговая схема, которая отличается от цифровых. Он требует гораздо больше навыков в проектировании схем/шаблонов и производстве компонентов.

Характеристики подложки радиочастотных модулей

- Форма полосы

- Толстая медь

- Контроль импеданса

- Строгий контроль однородности

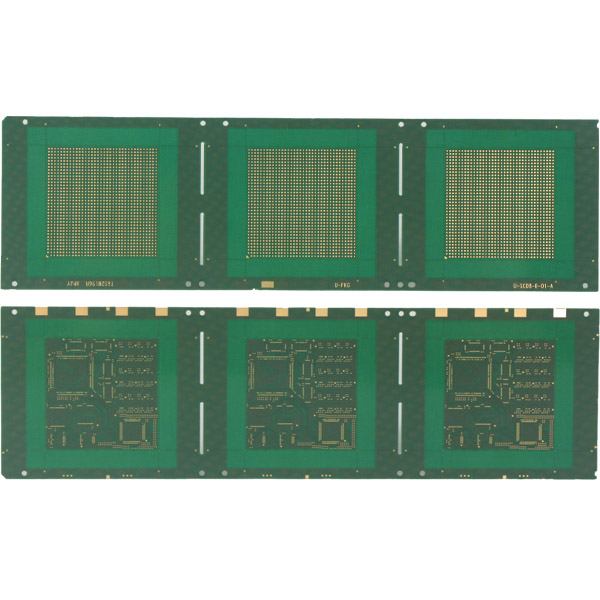

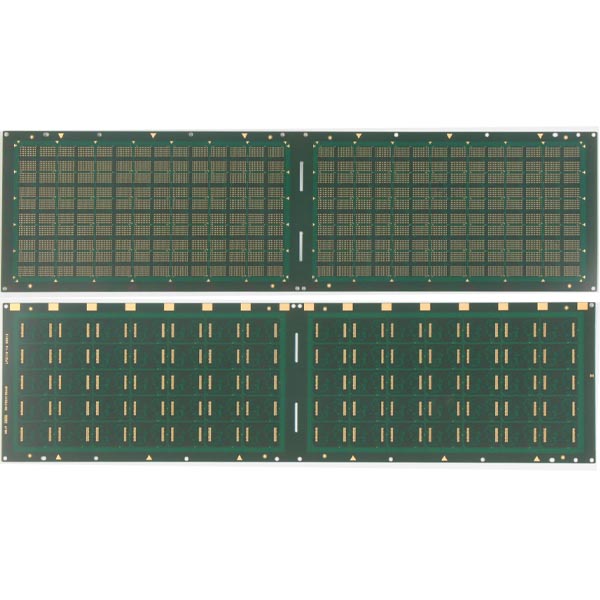

Подложка корпуса PBGA (пластиковая шариковая решетка)

PBGA (Plastic Ball Grid Array) выражает структурные характеристики подложки корпуса. Другими словами, на обратной стороне печатной платы вместо выводов выстраиваются шарики припоя для соединения подложки с основной платой. Термин PBGA используется так же широко, как и подложка корпуса.

Типичная подложка BGA для применения в корпусе ИС с проволочным соединением основана на ламинате с медным покрытием, пропитанным стекловолокном. Корпус PBGA является экономически эффективным решением для широкого диапазона числа входов/выходов микросхем. Когда функциональность ИС обновляется, она всегда переходит от корпуса с выводной рамкой к корпусу BGA.

Характеристики подложки корпуса PBGA

- Форма полосы

- Множественная отделка поверхности

- Широкий выбор материалов

- Оптимизация конструкции подложки с учетом тепловых и электрических характеристик

- Более мелкий шаг шариков и более тонкая толщина корпуса

- Высокие электрические характеристики благодаря короткой длине провода

- Процесс обратного травления

- Доступно как для Flip-chip, так и для Wire-склеивания

- Высокая плотность разводки с помощью полуаддитивного процесса

- Формирование тонкого рисунка для склеивания на технологии трассировки

- Стабильность размеров подложки для корпуса на корпусе

- Безвыводная конструкция пластины для межсоединений

Применение подложки корпуса PBGA

- ASIC, DSP и память, вентильные матрицы,

- Микропроцессоры / Контроллеры / Графика

- Компьютерные чипсеты и периферийные устройства

- Графические процессоры

- Телевизионные приставки

- Игровые консоли

- Gigabit Ethernet

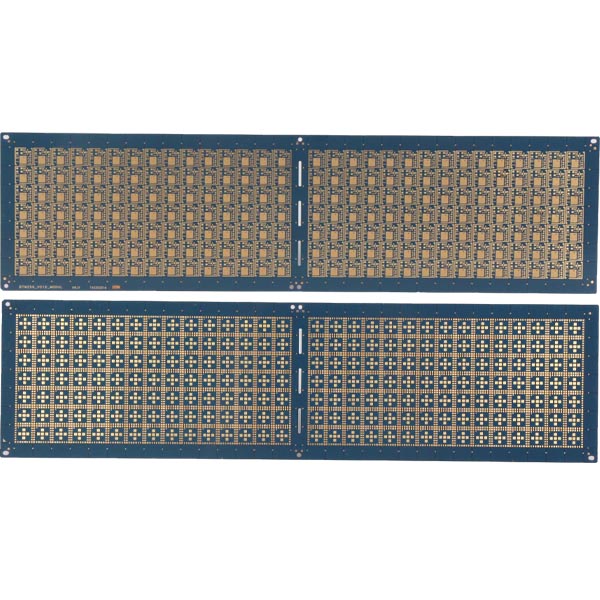

Подложка пакета FCCSP

CSP (Chip Size Package) — это продукт, размер подложки корпуса которого не превышает 120% размера полупроводникового кристалла. Чтобы уменьшить размер области, формируется CSP с высокоплотной разводкой по сравнению с обычным BGA. Самая важная цель CSP — уменьшить размер области монтажа.

Это называется Flip Chip Chip Scale Package (FCCSP), поскольку полупроводниковые кристаллы перевернуты и подключены к плате через выступ, а не через проводное соединение. Он в основном используется для микросхем прикладных процессоров (AP) мобильных ИТ-устройств. Также по сравнению с WBCSP с использованием золотой проволоки, процесс с использованием Flip Chip может применяться к полупроводникам высокой плотности, поскольку маршрут электрических сигналов короче, и можно разместить больший вход и выход.

Характеристики подложки пакета FCCSP

- Отдельный блок или полоса

- Мелкий шаг, процесс mSAP

- Тонкая и плоская доска

- Процесс без сердечника

FCCSP Package Substrate Application

- EEPROM. Флэш-память NAND, управление питанием, интегрированные пассивные сети, стандартное аналоговое устройство

- PRAM, LPDDR,ONEDRAM, Флэш-память NAND

- Мобильные телефоны, КПК, ноутбуки, дисководы, цифровые камеры, MP3-плееры, GPS-навигаторы, питьевые продукты

Корпус Flip Chip CSP (fcCSP) компании Hemeixin — решение с перевернутым кристаллом в формате корпуса CSP. Эта конструкция корпуса совместима со всеми нашими доступными вариантами выводов (медный столб, бессвинцовый припой, эвтектика), при этом обеспечивая технологию межсоединений Flip Chip в массиве областей и, при замене стандартного межсоединения Wirebond, в периферийной компоновке выводов. Преимуществ межсоединения Flip Chip несколько: оно обеспечивает улучшенные электрические характеристики по сравнению со стандартной технологией Wirebond, позволяет использовать меньший форм-фактор за счет повышенной плотности маршрутизации и устраняет влияние высоты z петель проводных соединений.

Корпус fcCSP собирается на ламинированной или литой подложке с сердечником или без него. Корпус обрабатывается в формате полосы для эффективности производства и минимизации затрат, а также позволяет использовать структуры с голым кристаллом, переформованным и открытым кристаллом. Тепловые проблемы мощных устройств можно решить, применив интегрированный теплоотвод. Антенна в корпусе (AiP) может быть включена с использованием крепления чипа с нижней стороны. Наконец, в сочетании с медным столбчатым кристаллом с выступами технология fcCSP использует преимущества тонкой трассировки подложки линий/пространств и шага выступов для уменьшения количества слоев и стоимости при одновременном повышении электрических характеристик.

Корпус fcCSP является привлекательным вариантом для приложений, в которых важны как производительность, так и форм-фактор. Примерами служат высокопроизводительные мобильные устройства (включая 5G), информационно-развлекательные системы и ADAS для автомобилей, а также искусственный интеллект. Кроме того, преимущества низкой индуктивности и повышенной плотности маршрутизации позволяют оптимизировать электрические пути для высокочастотных сигналов, что делает fcCSP подходящим для приложений с базовой полосой, радиочастотами и антеннами в подложке.

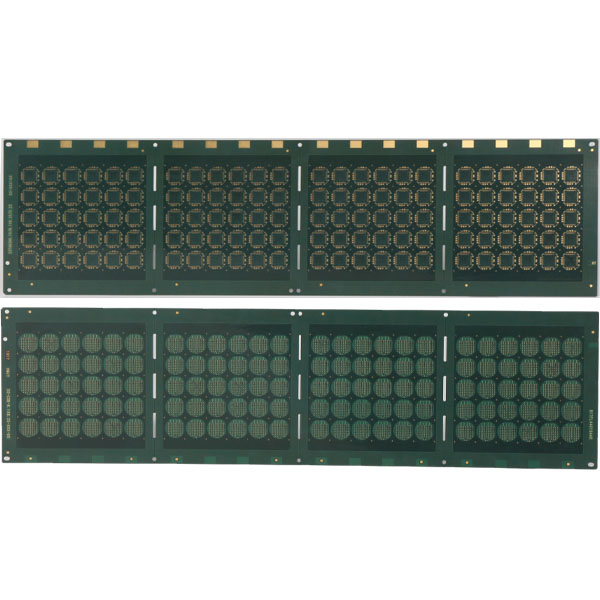

Подложка корпуса FCBGA

FCBGA (Flip-Chip Ball Grid Array), который использует высокоплотные микровыступы для соединения цифровых чипов и подложки с помощью процесса Flip Chip и размещения пассивных устройств рядом с чипами на поверхности подложки, чтобы сформировать тип корпуса BGA (Ball Grid Array) или LGA (Land Grid Array). Hemeixin использует технологию SAP (полуаддитивный процесс) для производства подложки FCBGA с высокой плотностью и большим количеством слоев для поддержки высококачественных перевернутых чипов и обеспечения высокоэффективного электрического соединения и высокоскоростной передачи.

Подложки FCBGA представляют собой полупроводниковые корпуса с точным правилом проектирования и высокой надежностью. Hemeixin предоставляет корпуса ИС с более чем 3000 входов/выходов, которые соответствуют следующему поколению перевернутых кристаллов LSI, использующих передовые правила проектирования и самые современные технологии обработки.

Продукт представляет собой высокоинтегрированную подложку корпуса, которая используется для соединения высокоинтегрированного полупроводникового чипа с основной платой. Это высокоинтегрированная плата корпуса, которая улучшает электрические и тепловые характеристики за счет соединения полупроводникового чипа и платы корпуса с помощью Flip Chip Bump. Кроме того, высокая интеграция схемы платы ЦП требует увеличения количества слоев платы и точного согласования между слоями; в то же время требуется возможность изготовления тонких плат для более тонких наборов.

Особенности подложки корпуса FCBGA

- Лидеры в схемотехнике, правило как линия/пространство: 9 мкм/12 мкм

- Усовершенствованное формирование малых переходных отверстий с помощью технологии лазерных переходных отверстий

- Используется высоконадежная термореактивная эпоксидная смола

- Доступны различные варианты отделки поверхности (Ni/Au, пайка SAC и т. д.)

- Применимые экологически чистые продукты (без галогенов, без свинца)

- 4~16 слоев накладываются друг на друга для реализации требований к высокой плотности соединений передового процесса пластин

- Высокоточная, высокоплотная лазерная технология микропереходных отверстий с превосходной возможностью выравнивания

- Ball Grid Array (BGA) или Land Grid Array (LGA) используют эту технологию для подключения к кристаллу

- Чтобы использовать процесс SAP для обеспечения высокой точности и высокой плотности тонких линий

- Технология uBall используется для размещения до десятков тысяч микрошариков Sn на верхней поверхности подложки. Эти шарики Sn используются для соединения с микровыступом на поверхности кристалла перевернутого кристалла

Корпуса Hemeixin Flip Chip BGA (FCBGA) собираются вокруг современных, цельных ламинированных или керамических подложек. Используя несколько слоев маршрутизации высокой плотности, лазерное сверление глухих, скрытых и многослойных переходных отверстий и сверхтонкую металлизацию линий/пространств, подложки FCBGA имеют самую высокую доступную плотность маршрутизации. Благодаря сочетанию межсоединений перевернутого кристалла с ультрасовременной технологией подложки, корпуса FCBGA могут быть электрически настроены для максимальной электрической производительности. После определения электрической функции гибкость конструкции, обеспечиваемая перевернутым кристаллом, также обеспечивает значительные возможности в окончательном дизайне корпуса. Hemeixin предлагает корпус FCBGA в различных форматах продукта, чтобы соответствовать широкому спектру требований конечного применения.

Процесс производства подложек BGA-корпуса

Что такое полуаддитивный процесс?

Технологии полуаддитивного процесса (SAP):

Электронная промышленность быстро движется в сторону более мелких шагов, чтобы обеспечить более высокую скорость, требуемую от компонентов. Мы наблюдали переход от шага 1 мм к шагу 0,8, 0,5, 0,4 и теперь 0,25 мм. В то же время увеличивается количество требуемых входов/выходов. Мы начали видеть рост конструкций с линиями и интервалами менее 50 мкм (0,002 дюйма). Традиционные методы формирования дорожек не позволят производить эти печатные платы с разумной производительностью.

Преимущества:

- Уменьшение размера и веса на 90% по сравнению с текущим уровнем техники в Китае

- Эффективное сокращение количества слоев и циклов ламинирования

- Значительные преимущества в области радиочастот по сравнению с традиционными процессами субтрактивного травления

- Повышенная плотность электроники в фиксированной области

Технические документы:

- Исследование надежности и производительности материалов

- Надежность стековых микроотверстий

- Покрытие оберткой

- Устранение неполадок микроотверстий

Технология структурирования проводников для обеспечения сверхтонкой проводки

Сосредоточившись на SAP (полуаддитивный процесс), мы обеспечиваем микроструктурирование мирового класса. Мы также способствуем развитию технологий структурирования проводников полупроводникового превосходства в будущем.

mSAP – модифицированный полуаддитивный процесс

mSAP – модифицированный полуаддитивный Миниатюризация и новые требования рынка требуют разработки инновационных решений для того, чтобы предоставить нашим клиентам наилучшие возможные технологии производства в будущем. Одним из таких нововведений для удовлетворения растущего спроса в области тонких печатных плат является наша деятельность по разработке модифицированного полуаддитивного процесса (mSAP).

Технология mSAP позволяет создавать гораздо более тонкие структуры вплоть до 25 мкм линии/пространства. Кроме того, этот процесс обеспечивает значительно лучшую геометрию рисунка проводника. Для высокочастотных приложений это дает большие преимущества в производительности. Эта технология также может дать решающие преимущества для печатных плат интерпозеров и высокоскоростных печатных плат.

В традиционном субтрактивном процессе структуры создаются путем ламинирования, экспонирования и проявления фоторезиста в качестве защиты от травления на поверхности меди. Затем незащищенная медь удаляется травильной средой. В Hemeixin таким образом с высокой надежностью можно изготавливать рисунок проводника размером 50 мкм и больше.

Если необходимо сформировать более тонкие схемы проводников, субтрактивный процесс достигает своих пределов. Одним из решений этой проблемы является полуаддитивный процесс, который долгое время использовался в полупроводниковой промышленности и теперь становится все более важным в производстве печатных плат. Поскольку описанный вариант является модифицированной версией, этот процесс называется модифицированным полуаддитивным процессом (mSAP).

В процессе mSAP на ламинат наносится только тонкий слой меди. Затем наносится фотоструктурируемый твердый резист, а макет экспонируется и проявляется в перевернутом виде. Требуемая толщина меди добавляется к экспонированным медным областям в процессе гальванопокрытия. После удаления твердого резиста тонкий начальный слой меди удаляется дифференциальным травлением.

Наш выбор продукции для модифицированного полуаддитивного процесса (mSAP) для схем высокой плотности увеличивает выход продукции и позволяет создавать новые конструкции. mSAP — это экономически эффективный процесс для тонких линейных подложек, который обеспечивает высокую степень автоматизации, высокую производительность и бережливое производство. Hemeixin Electronics Co.,Ltd имеет портфолио, которое охватывает все этапы процесса, включая формирование схемы, гальванопокрытие медью, травление и финальную отделку.

Поскольку для охвата всех функций, необходимых для современных мобильных устройств, подложек ИС и печатных плат (ПП) с подложкой требуются более высокие плотности, производители начали полагаться на mSAP для удовлетворения своих проектных требований. Надежные технологии, которые могут обеспечить выход и качество, необходимые для этой сложной производственной парадигмы, предлагаются только поставщиками химикатов с техническими знаниями и технологическими возможностями для поставки.

WWPCB предлагает полный набор специальных решений для производства с использованием mSAP высокой плотности, что позволяет нашим клиентам достигать результатов, которых они в противном случае не смогли бы достичь с помощью обычной технологической химии. Наши технологии восстановления меди позволяют точно настраивать толщину медной фольги, в то время как наши процессы предварительной обработки внутреннего слоя и лазерного сверления обеспечивают высокую скорость сигнала и жесткие допуски переходных отверстий. Наши процессы прямой металлизации с низким травлением позволяют уменьшить количество медных интерфейсов и повысить качество разрешения тонких линий за счет уменьшенного травления. Наши передовые технологии гальванопокрытия медью позволяют создавать тонкие линии и пространства с нулевой планаризацией между слоями и даже устранять v-питтинг без необходимости запекания панелей после нанесения покрытия.

Наше финишное травление с высоким разрешением определяет следы с превосходными профилями боковых стенок и нулевым подрезом, а наш выбор финишных покрытий предлагает широкий спектр функциональных поверхностей для удовлетворения требований к сборке. Глобальные производители оригинального оборудования (OEM) устройств используют наши передовые производственные процессы для mSAP для питания следующего поколения высокопроизводительных электронных устройств, которые производятся сегодня.Процесс