Введение: Решение проблем целостности сигнала (SI) на ранних этапах проектирования может значительно упростить процесс, устранив необходимость в корректирующих компонентах на поздних стадиях. В этой статье описаны ключевые шаги для поддержания SI — от начального планирования до финального тестирования.

1. Подготовка перед проектированием

Определите требования к SI и стратегию проектирования заранее. Такое планирование направляет выбор компонентов, устанавливает производственные допуски и позволяет контролировать затраты, избегая таких распространенных проблем SI, как перекрестные помехи и задержки.

2. Планирование стека печатной платы

Внимательно продумайте структуру слоев (стек) печатной платы. Производственные допуски, диэлектрические свойства и целевой импеданс влияют на качество SI. Сотрудничайте с производителями для оптимизации стека, включая слои с контролируемым импедансом и пары плоскостей заземления/питания для снижения помех.

3. Контроль перекрестных помех и импеданса

Перекрестные помехи от соседних сигнальных линий могут нарушить импеданс. Анализ взаимного влияния поможет установить безопасное расстояние между критическими линиями, особенно в высокоскоростных схемах, обеспечивая стабильность импеданса.

4. Определение ключевых высокоскоростных узлов

Маршрутизация таких высокоскоростных узлов, как тактовые линии, требует минимального перекоса для соблюдения временных требований. Предусмотрите для них особую разводку и компоненты окончания, чтобы поддерживать оптимальный уровень SI.

5. Выбор технологии привода

Определите соответствующую технологию привода на основе параметров сигнала и длины трассировки. Низкие скорости нарастания могут улучшить SI, уменьшив шум. Рассмотрите использование FPGA или ASIC, оптимизируя их параметры для достижения нужного баланса между производительностью и целостностью сигнала.

6. Планирование предварительной разводки

Применяйте инструменты моделирования, чтобы оценить возможные конфигурации на этапе предварительной разводки. Настраивайте параметры и ограничения разводки, чтобы заложить фундамент для оптимальной SI перед размещением компонентов.

7. Моделирование SI после трассировки

После завершения трассировки выполните пост-компоновочное моделирование, чтобы проверить соответствие требованиям SI. Это позволит вовремя скорректировать проект и устранить ошибки до этапа производства.

8. Тестирование после производства

Используйте осциллограф или TDR для сравнения реальных характеристик платы с моделируемыми данными. Результаты помогут улучшить будущие проекты и принимать менее жесткие, но надежные проектные решения.

9. Выбор модели

Для точного моделирования необходимы надежные модели компонентов, чаще всего предоставляемые производителями ИС. Модели IBIS предпочтительны для обеспечения точности, но их создание может быть дорогостоящим. Поддерживайте сотрудничество с поставщиками для получения качественных данных.

10. Постоянное совершенствование

Внедряйте обратную связь из постпроизводственного тестирования для улучшения SI-практик. Каждая итерация дизайна повышает точность моделей и улучшает процесс проектирования, обеспечивая высокое качество SI в будущем.

Эффективное обеспечение SI — это основа для стабильной работы печатной платы, особенно в высокоскоростных приложениях. Следуя этим шагам, вы сможете оптимизировать качество сигнала и обеспечить долговечность и надежность своих проектов.

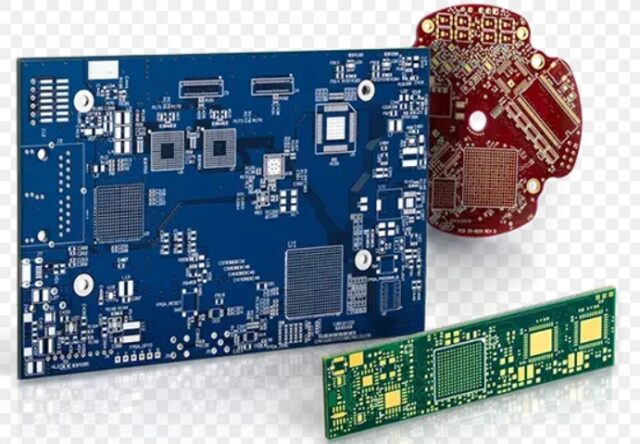

KKPCB предоставляет глобальным клиентам комплексные услуги от макета печатной платы, прототипа печатной платы, производства печатных плат, обработки печатных плат (включая SMT и DIP), тестирования печатных плат, сборки печатных плат и исходящей упаковки. Вы можете предоставить нам файл Gerber или список BOM, мы предложим готовые печатные платы или сборку печатных плат, которые вас устраивают.