С уменьшением размеров электронных устройств и развитием технологий компонентов и проводки возникли новые проблемы для тестирования на этапе производства. Высокая степень интеграции микросхем, сокращение расстояния между проводниками и ограниченный доступ к узлам цепи делают традиционные методы тестирования недостаточными. Для решения этих задач необходим подход «проектирование для тестирования» (DFT), который помогает снизить затраты на тестирование и повысить эффективность производства. В этом руководстве рассматриваются принципы, стратегии и лучшие практики по улучшению тестопригодности печатных плат.

HomeTag

Печатная плата

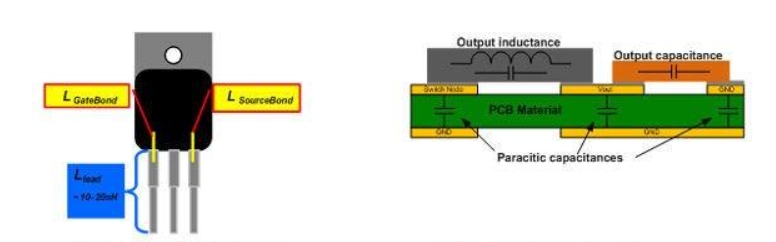

Суперсоединительные MOSFET становятся всё более востребованными в приложениях, где ключевым является улучшение эффективности. Благодаря низкому сопротивлению канала и уменьшенной паразитной ёмкости они идеально подходят для использования в схемах, где обычные MOSFET на базе планарной технологии могут не справляться. Однако быстрая коммутация суперсоединительных MOSFET приводит к высокочастотным шумам и радиационным помехам из-за резких переходов напряжения (dv/dt) и тока (di/dt). Тщательный подход к проектированию печатной платы и оптимизация схемы помогут полностью раскрыть потенциал данных транзисторов без потери производительности.